## Formation of selfaligned holes in an arbitrary pattern in silicon substrate

HiDeok Lee, HoJun Lee, ChoongKi Kim, and ChulHi Han

Citation: Appl. Phys. Lett. 66, 3272 (1995); doi: 10.1063/1.113401

View online: http://dx.doi.org/10.1063/1.113401

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v66/i24

Published by the American Institute of Physics.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

## **ADVERTISEMENT**

## Formation of self-aligned holes in an arbitrary pattern in silicon substrate

Hi-Deok Lee, <sup>a)</sup> Ho-Jun Lee, Choong-Ki Kim, and Chul-Hi Han Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Kusong-dong 373-1, Yusong-gu, Taejon 305-701, Korea

(Received 8 December 1994; accepted for publication 23 March 1995)

A self-aligning etch method for silicon substrates is presented. A hole pattern is defined on the front side of the silicon substrate while etching of the hole takes place from the back side through the application of a current from the front side of the silicon substrate to a cathode electrode in a solution of HF, HNO<sub>3</sub>, and H<sub>2</sub>O. As the etching proceeds, the etched pattern in the back side gradually becomes self-aligned with the front side pattern of the silicon substrate. Twenty five circular holes arranged in a  $5\times5$  array are formed in a boron-doped (100) silicon substrate. The etch method provides control over hole dimensions which are  $520~\mu m$  in diameter and spaced  $520~\mu m$  apart. The self-aligning property of the etch method enables the formation of different shaped holes. © 1995~American~Institute~of~Physics.

In recent years, significant interest has been shown in silicon micromachining and specifically silicon etching. Silicon has excellent mechanical properties as well as electrical properties which enable the integration of mechanical and electrical devices on the same chip. Furthermore, silicon technology has the advantages of batch-fabrication capability, low cost, miniaturization, and reproducibility of device characteristics. The increasing importance of silicon micromachining, especially of bulk micromachining, has generated growing interest in etching through silicon substrates while maintaining precise control of microstructural dimensions and position.<sup>1-3</sup> To date, conventional orientationdependent etching methods have been widely used to etch the silicon substrate using aqueous KOH,4,5 ethylenediamine, 6,7 and hydrazine. 8,9 In conventional orientationdependent methods, the final size of the etched hole cannot be defined exactly on the front side of the substrate because the pattern of etching is formed on the back side of the silicon substrate. Furthermore, the pattern requires exact alignment to the specific crystallographic axes of silicon. Another disadvantage is that only a few limited geometries of a hole can be realized on the silicon substrate.3 Thus, an etching method which can define the pattern on the front side of the silicon substrate and etch through silicon without orientational dependence is highly desirable.

In this letter, we propose a method to overcome the limitations of conventional etching techniques. In this new method, the pattern of etching is defined on the front side of the silicon substrate while the etching takes place from the back side and aligns itself with the front side pattern. The silicon etch is done by an anodic dissolution method with neither a pattern nor a special treatment on the back side of the silicon substrate. Many studies have been performed on the anodic dissolution of silicon in the HF–H<sub>2</sub>O system,  $^{10-12}$  but none has addressed the formation of holes using the anodic dissolution method.

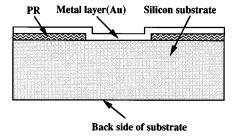

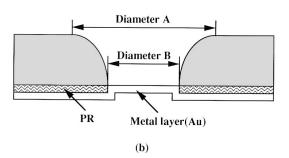

A boron-doped (100) silicon wafer with a resistivity of  $5{\text -}10~\Omega$  cm and a thickness of  $505{\text -}545~\mu\text{m}$  was used in this experiment. A schematic cross section of the silicon substrate

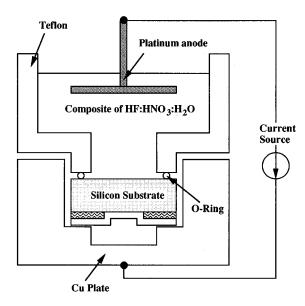

prior to etching is shown in Fig. 1. Photoresist is used as a insulating layer between the metal layer and the silicon substrate. The front side etch pattern is formed by the contact between metal with the silicon substrate. The metal film is deposited on the patterned photoresist so that etching can occur only in the area electrically contacted to the metal layer. The back side of the silicon substrate is not polished or patterned prior to etching. Au was chosen for the metal layer for its durability under corrosive environments and its ability to adhere well to both silicon and photoresist. Two types of samples were prepared for experiments. Sample A has a rectangle pattern of 5 mm×5 mm and sample B has 25 circular patterns arranged in a 5 $\times$ 5 array. Each circle is 520  $\mu$ m in diameter and spaced 520 µm apart. The experimental arrangement for etching the samples is shown in Fig. 2. In this arrangement, the silicon substrate is placed upside down under the Teflon vessel where only the back side of the substrate is in contact with the etchant while the rest of the silicon sample is sealed from the etchant by a silicone O-ring. A constant current is applied from the front side of the substrate to the platinum cathode electrode which is placed 2 cm apart from the exposed silicon substrate surface. The etchant formula is 1:1:1 HF(48%-51%):HNO<sub>3</sub>  $(69\%-71\%):H_2O$  by volume.

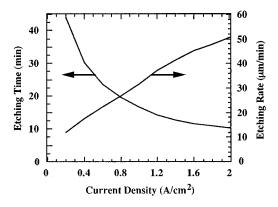

Figure 3 shows the etching characteristics obtained using sample A. The anodic dissolution of silicon begins as soon as the current is applied. The etching rate is nearly proportional to the applied current and the etching time is inversely pro-

FIG. 1. Schematic cross section of a silicon sample used in this experiment. The photoresist is 1.2  $\mu$ m thick and Au is 2000 Å thick. A boron-doped (100) silicon wafer with a resistivity of 5–10  $\Omega$  cm and a thickness of 505–545  $\mu$ m is used.

a) Also with LG Semicon (Formerly Goldstar Electron) Co., Ltd.

FIG. 2. Experimental arrangement for etching the silicon substrate. The back side of the silicon substrate is in contact with the solution of 1:1:1 HF(48%-51%):HNO<sub>3</sub>(69%-71%):H<sub>2</sub>O by volume. The platinum cathode is placed 2 cm apart from the silicon wafer.

portional to the applied current as shown in Fig. 3. The etching rate of this method is faster than those of other conventional anisotropic etching methods.

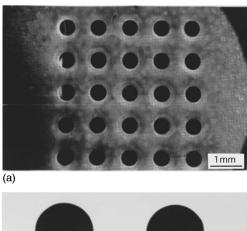

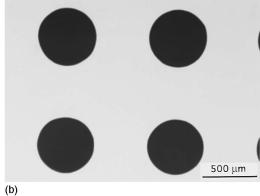

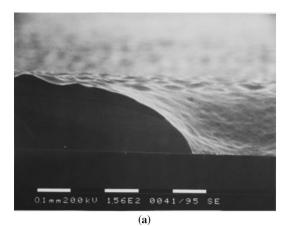

Figure 4 shows a SEM micrograph and a photomicrograph of the etched sample B with an applied current of 68 mA. The average current density is 1.28 A/cm<sup>2</sup> if the current is uniformly distributed over the pattern area of the front side. Accurate and well-defined circular holes are obtained on the front side of the silicon substrate as can be seen in the cross-sectional view of an etched hole in Fig. 5. The shape of the etched hole shows that the etched pattern gradually converges to the front pattern of the silicon substrate. The etched area (diameter A) on the back side of the substrate is larger than the pattern (diameter B) on the front side of the substrate as shown in Fig. 5(b). This effect is due to the positive feedback seen by the anodic current density during etching. In the beginning of etching, the reaction area on the back side of the substrate (diameter A) becomes larger than the pattern on the front side (diameter B). This is because the current applied to the silicon anode spreads out in the sub-

FIG. 3. Etching characteristics (etching time and etching rate vs current density) for a sample A.

FIG. 4. (a) SEM micrograph of the circular holes viewed from the back side of the substrate and (b) photomicrograph viewed from the front side after the silicon substrate is etched through.

FIG. 5. (a) SEM micrograph of the cross section and (b)schematic cross section of the etched silicon substrate.

Appl. Phys. Lett., Vol. 66, No. 24, 12 June 1995

Lee et al.

strate due to the electrical resistance of the silicon substrate. This reduces the current density and the etching rate. As dissolution continues, the electrical resistance becomes much smaller at the center part of the pattern which results in the enhancement of the current density and the dissolution rate of the substrate. The positive feedback effect makes the etched profile steeper in the front surface as shown in Fig. 5(a) and enables the etched surface to be self-aligned with the front side of silicon substrate.

In conclusion, a novel self-aligning etch method for silicon substrates has been proposed. Unlike conventional etch methods, accurately defined and controlled hole patterns can be self-aligned with already-fabricated devices or structures without regard to orientation of the substrate. The etching of silicon begins on the back side of the substrate in a solution of HF, HNO<sub>3</sub>, and H<sub>2</sub>O by the anodic dissolution method and the etched hole is self-aligned with the pattern on the front side of the substrate. Twenty five circular holes with a diameter of 520  $\mu$ m are accurately obtained on the front side of the silicon substrate of a thickness of 505–545  $\mu$ m. The self-aligning property enables the formation of various patterns of holes. Furthermore, allowing the etchant to only con-

tact the back side of the substrate protects the mechanical and electrical devices fabricated prior to the etch from the corrosive silicon etchant. This method can be widely applied in bulk micromachining such as in microchannel formation.

The authors would like to thank J. D. Lee, J. K. Kim, J. B. Yoon, K. H. Han, S. W. Lee, and D. W. Seo for their helpful discussions.

<sup>&</sup>lt;sup>1</sup>E. Bassous, H. H. Taub, and L. Kuhn, Appl. Phys. Lett. **31**, 135 (1977).

<sup>&</sup>lt;sup>2</sup>E. Bassous and E. F. Baran, J. Electrochem. Soc. **125**, 1321 (1978).

<sup>&</sup>lt;sup>3</sup>S. C. Terry, J. H. Jerman, and J. B. Angell, IEEE Trans. Electron Devices ED-26, 1880 (1979).

<sup>&</sup>lt;sup>4</sup>D. F. Weirauch, J. Appl. Phys. **46**, 1478 (1975).

<sup>&</sup>lt;sup>5</sup>E. D. Palik, V. M. Bermudez, and O. J. Glembocki, J. Electrochem. Soc. 132, 871 (1985).

<sup>&</sup>lt;sup>6</sup>R. M. Finne and D. L. Klein, J. Electrochem. Soc. **114**, 965 (1967).

<sup>&</sup>lt;sup>7</sup> A. Reisman, M. Berkenblit, S. A. Chan, F. B. Kaufman, and D. C. Green, J. Electrochem. Soc. **126**, 1406 (1979).

<sup>&</sup>lt;sup>8</sup>D. B. Lee, J. Appl. Phys. **40**, 4569 ((1969).

<sup>&</sup>lt;sup>9</sup> M. J. Declercq, L. Gerzberg, and J. D. Meindl, J. Electrochem. Soc. 122, 545 (1975).

<sup>&</sup>lt;sup>10</sup>D. R. Turner, J. Electrochem. Soc. **105**, 402 (1958).

<sup>&</sup>lt;sup>11</sup>X. G. Zhang, S. D. Collins, and R. L. Smith, J. Electrochem. Soc. **136**, 1561 (1989).

<sup>&</sup>lt;sup>12</sup>R. L. Smith and S. D. Collins, J. Appl. Phys. 17, R1 (1992).