# **Reliability Study of CMOS FinFETs**

Yang-Kyu Choi, Daewon Ha, Eric Snow, Jeffrey Bokor, and Tsu-Jae King

Department of Electrical Engineering and Computer Sciences

University of California, Berkeley, CA 94720, USA

E-mail: ykchoi@eecs.berkeley.edu, Tel:+1-510-643-2558, Fax:+1-510-643-2636

## Abstract

Hot-carrier and oxide reliability of CMOS FinFETs with 2.1 nm-thick gate-SiO<sub>2</sub> were investigated. It was found that hot-carrier immunity improves as the fin width (body thickness) decreases, which facilitates gate-length scaling, while it is degraded at elevated temperature due to the self-heating effect. High values of  $Q_{BD}$  are achieved for devices with very small gate area. A post-fin-etch hydrogen anneal is helpful for improving hot-carrier immunity and  $Q_{BD}$ .

## Introduction

The FinFET offers the superior scalability of the double-gate MOSFET structure with a conventional process flow; hence, it is attractive for scaling CMOS technology to sub-10nm gate lengths. Several groups have recently reported on the fabrication and performance of CMOS FinFET devices [1]-[4]. In this work, the reliability of FD-SOI CMOS FinFETs is investigated. Hot-carrier reliability for various bias stress conditions, device dimensions, and substrate temperature are reported. Gate oxide charge-to-breakdown (QBD) distributions are also presented.

# Experiment

Fabrication process details for the FinFETs used in this work have already been reported elsewhere [1][5]. Two different types of FinFETs were investigated: P+ poly-Si<sub>0.6</sub>Ge<sub>0.4</sub> gated FinFETs with gate lengths down to 23nm, fabricated using e-beam lithography (Group I); and N+ poly-Si gated FinFETs of gate length 120nm, fabricated using spacer lithography (Group II). In Group II, one wafer was annealed in hydrogen (5min @ 900°C and latm) to smoothen the fin sidewall surfaces prior to gate oxidation [5]. The gate dielectric in all devices was 2,1nm thermally grown SiO2. For Group I, significant boron penetration through the gate oxide into the channel/fin resulted in a high threshold voltage (V<sub>T</sub>=0.8V) and gateunderlapped structure for the n-channel FinFETs. (The pchannel FinFETs have a conventional gate-overlapped structure.) This work is primarily focused on the reliability of sub-100nm L<sub>e</sub> FinFETs (Group I). Only the effects of post-fin-etch annealing in  $H_2$  were studied using the longer-channel devices from Group II.

First, the worst-case bias condition for hot-carrier stress was determined, for  $V_d=1.8V$ . The  $V_T$  shift was found to be larger when the gate voltage was equal to the drain voltage ( $V_g=V_d$ ), compared to  $V_g=V_d/2$ . Degradation in device performance parameters under  $V_g=V_d=1.8V$  stress was then tracked over time, for FinFETs of various gate lengths and fin widths ( $W_{fin}$ ), and several substrate temperatures.  $Q_{BD}$  distributions were also obtained for FinFETs of various sizes.

## Results

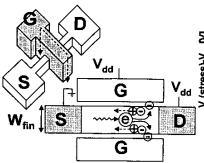

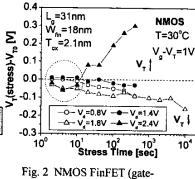

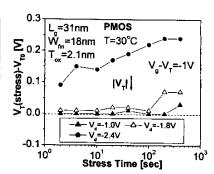

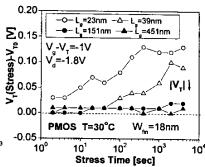

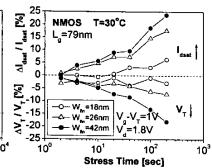

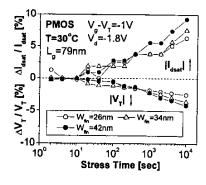

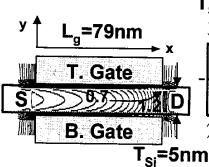

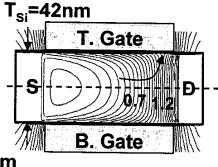

In a double-gate n-channel MOSFET, energetic electrons generated by impact ionization near the drain can become trapped at the gate-oxide interface or in the gate oxide to cause an increase in V<sub>T</sub>, while the generated holes flow to the region of lowest potential (i.e. the source), as shown in Fig. 1. For gate-underlapped n-channel FinFETs, holes can become trapped at the gate-oxide interface in this region, causing a decrease in V<sub>T</sub>. Thus, electron trapping and hole trapping have opposite effects on V<sub>T</sub>. For fixed  $V_g$ - $V_T$ =1V, the dominant  $V_T$ -shift mechanism depends on  $V_d.$  Hole trapping is dominant for  $V_d{\le}1.8V,$  so that the magnitude of  $V_{\text{T}}$  decreases with increasing stress time, while electron trapping becomes dominant at higher values of  $V_d$ , so that  $V_T$  eventually increases with increasing stress time (Fig. 2). For gate-overlapped pchannel FinFETs, the magnitude of V<sub>T</sub> decreases consistently with increasing |V<sub>d</sub>| (Fig. 3), similar to the behavior of bulk-Si PMOSFETs.

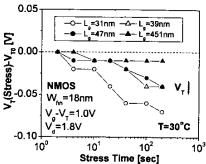

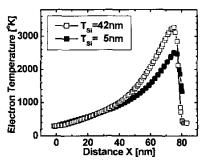

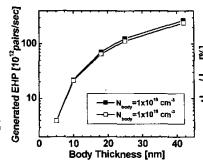

The magnitude of the  $V_T$  shift decreases with increasing channel length (Fig. 4 and Fig. 5) due to the decreasing lateral electric field; however it increases with increasing fin width, as shown in Fig. 6 and Fig. 7. To explain this dependence on  $W_{\rm fin}$ , the electron-hole pair generation rate (G) – due to impact ionization – and electron temperature ( $T_e$ ) profile in an n-channel double-gate MOSFET were studied using the device simulator MEDICI [6]. The gate is assumed to be perfectly aligned (zero overlap) to the abrupt source/drain (S/D) junctions, and its doping concentration is  $2 \times 10^{20} \text{cm}^{-3}$ . The simulation results (Figures 8-11) show that both  $T_e$  and G increase with increasing  $W_{\text{fin}}$ , which is consistent with the reliability measurement data. Figs. 8 and 9 show that the potential profile becomes increasingly "one-dimensional" as the

body thickness decreases. In the thicker body case, hot electrons are more strongly driven towards the gate oxide by the 2D curvature of the potential. The paths of generated hot carriers are indicated schematically by the bold arrows in Figs. 8 and 9. Thus, hot-carrier immunity is improved by thinning the body of a double-gate MOSFET, which also improves short-channel effects. The simulations show that G is insensitive to channel (fin) doping concentration (Fig. 11).

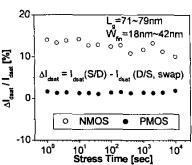

Degradation of the drain saturation current (I<sub>deat</sub>) is observed after swapping the source and drain during device measurement after each stress interval, as shown in Fig. 12. The degradation is more significant in an nchannel FinFET (n-FinFET) than a p-channel FinFET (p-FinFET) because the n-FinFET has an underlapped-gate structure and p-FinFET has an overlapped-gate structure. More hot carriers are trapped in the underlapped region. The trapped electrons at the drain, which becomes the source after the swapping, suppress the inversion charge. They result in an increase in V<sub>T</sub>, hence a decrease in I<sub>dsat</sub>. In the n-FinFET,  $I_{dsat}$  is degraded 4.6% for  $W_{fin}$  =18nm and 24% for W<sub>fin</sub> =42nm. This proves that more carriers are trapped for a thick body as compared with a thin body, consistent with the simulation results shown in Fig. 8 and Fig. 9, and also consistent with the improved hot-carrier immunity observed for a thinner body.

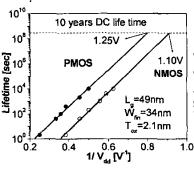

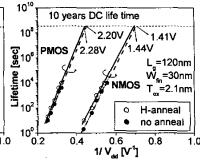

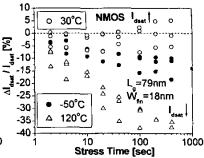

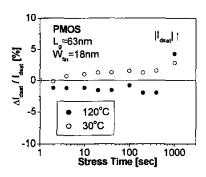

Hot-carrier DC lifetime is plotted in Fig. 13 and Fig. 14. The criteria for failure used for these plots are 10% change of V<sub>T</sub>, 10% change of g<sub>m</sub> (transconductance), and 10% change of I<sub>dsat</sub>. Ref. 3 also reports hot-carrier DC lifetime results for FinFETs. However, the results presented here are not directly comparable to the previously reported results because the oxide thicknesses are different and the failure criteria were not noted. The lifetime is improved slightly for devices that received a post-fin-etch anneal in H<sub>2</sub> (Fig. 14). These results indicate that FinFETs should be able to meet the 10-yr lifetime requirement for normal operating conditions, if W<sub>fin</sub> is sufficiently small. The effect of substrate temperature during stress is shown in Fig. 15 and Fig. 16. Ordinarily, G increases when the temperature is decreased, because of increased mean free path [7]. Thus, worse degradation (due to electron trapping) is seen at -50°C compared to 30°C. At elevated temperatures, self-heating effects are significant in SOI MOSFETs and can enhance G [8]. Thus, we also find worse degradation (due to electron trapping) at 120°C vs. 30°C.

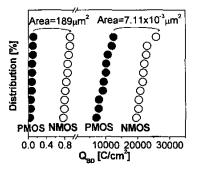

The gate voltage was linearly ramped for charge-to-breakdown ( $Q_{BD}$ ) measurements. The area of a single-fin device is  $7.11\times10^{-3}\mu\text{m}^2$  ( $L_g$ =79nm and fin height=45nm). The measured  $Q_{BD}$  is approximately  $10^4\text{C/cm}^2$  for these FinFETs with extremely small gate area (Fig. 17). Degraeve *et al.* [9] reported that  $Q_{BD}$  becomes a strong function of the channel area as the gate-oxide thickness decreases. A similar trend (increasing  $Q_{BD}$  as the channel area decreases) is also observed in this work, as shown in

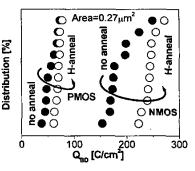

Fig. 17 and Fig. 18. Higher and more uniform  $Q_{BD}$  is achieved when a post-fin-etch anneal in  $H_2$  is employed (Fig. 18).

# **Summary**

The reliability of CMOS FinFETs has been studied. Hot-carrier immunity is found to improve with decreasing  $W_{fin}$ , and is degraded at high substrate temperature (120°C) due to the self-heating effect, as well as at low substrate temperature (-50°C). High values of  $Q_{BD}$  (>10<sup>4</sup> C/cm<sup>2</sup>) are achieved for 2.1nm gate oxide, for very small gate area. Hydrogen annealing to smoothen the fin sidewalls is effective for improving both hot-carrier lifetime and  $Q_{BD}$ .

## References

[1] Y.-K. Choi, N. Lindert, P. Xuan, S. Tang, D. Ha, E. Anderson, T.-J. King, J. Bokor, C. Hu, "Sub-20nm CMOS FinFET Technologies", *IEEE IEDM Technical Digest*, p.421-24, 2001.

[2] J. Kedzierski, D.M. Fried, E.J. Nowak, T. Kanarsky, J.H. Rankin, H. Hanafi, W. Natzle, D. Boyd, Y. Zhang, R.A. Roy, J. Newbury, C. Yu, Q. Yang, P. Saunders, C.P. Willets, A. Johnson, S.P. Cole, H.E. Young, N. Carpenter, D. Rakowski, B.A. Rainey, P.E. Cottrell, M. leong, H.-S. P. Wong, "High performance symmetric-gate and CMOS-compatible V, asymmetric-gate FinFET devices", *IEEE IEDM Technical Digest*, p.437-40, 2001.

[3] F.-L. Yang, H.-Y. Chen, F.-C. Chen, Y.-L. Chan, K.-N. Yang, C.-J. Chen, H.-J. Tao, Y.-K. Choi, M.-S. Liang, C. Hu, "35nm CMOS FinFETs", VLSI Tech. Dig., p.104-5, 2002.

[4] B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, D. Kyser, "FinFET Scaling to 10nm Gate Length", *IEEE IEDM Technical Digest*, p.251-4, 2002.

[5] Y.-K. Choi, L. Chang, P. Ranade, J.-S. Lee, D. Ha, S. Balasubramanian, A. Agarwal, M. Ameen, T.-J. King, J. Bokor, "FinFET Process Refinements for Improved Mobility and Gate Work Function Engineering", *IEEE IEDM Technical Digest*, p.259-262, 2002.

[6] MEDICI version 4.1, Avant! Coporation, 1998.

[7] M. Song, K.P. MacWilliams, J.C.S. Woo, "Comparison of NMOS and PMOS Hot Carrier Effects From 300K to 77K", *IEEE Trans. Electron Devices*, p.268-76, 1997.

[8] P. Su, K.-i. Goto, T. Sugii, C. Hu, "Enhanced Substrate Current in SOI MOSFETs", *IEEE Electron Device Lett.*, p.282-4, 2002.

[9] R. Degraeve, G. Groesenken, R. Bellens, J.L. Ogier, M. Depas, P.J. Roussel, H.E. Maes, "New Insights in the Relation Between Electron Trap Generation and the Statistical Properties of Oxide Breakdown", *IEEE Trans. Electron Devices*, p.904-11, 1998.

# Acknowledgement

This research is supported under MARCO contract 2001-MT-887 and SRC contract 2000-NJ-850.

Fig. 1 Schematic of FinFET, and carrier movement in an n-channel double-gate MOSFET under hot-carrier stress bias conditions.

Fig. 2 NMOS FinFET (gate-underlapped structure)  $V_T$  shift  $v_S$ . stress time for different drain bias stress voltages. Electron trapping eventually dominates for very high  $V_d$ .

Fig. 3 PMOS FinFET (gate-overlapped structure)  $V_T$  shift vs. stress time for different drain bias stress voltages.

Fig. 4 NMOS V<sub>T</sub> shift vs. stress time for different gate lengths. Longer-channel devices show better hot-carrier immunity due to the reduced lateral electric field.

Fig. 5 PMOS V<sub>T</sub> shift vs. stress time for different gate lengths. Longer-channel devices show better hot-carrier immunity due to the reduced lateral electric field.

Fig. 6 Relative shifts in  $V_T$  and  $I_{dset}$  for NMOS FinFETs (gate-underlapped structure) vs. stress time, for different fin widths. Better hot-carrier immunity is achieved with a narrower fin.

Fig. 7 Relative shifts in  $V_T$  and  $I_{dsat}$  for PMOS FinFETs (gate-overlapped structure) vs. stress time, for different fin widths. Better hot-carrier immunity is achieved with a narrower fin.

Fig. 8 Simulated 2-D potential profile in a double-gate MOSFET with  $L_g = 79$  and  $T_{Si} = 5$  nm. The gate is perfectly aligned (zero overlap) to the abrupt S/D junctions ( $N_{S/D}$ =2x10<sup>20</sup>cm<sup>3</sup>). The potential lines are more straight than for the thick-body device at the drain side.

Fig. 9 Simulated 2-D potential profile in a double-gate MOSFET with  $L_g = 79$  and  $T_{Si} = 42$  nm ( $V_g = V_d = 1.2V$ ). The highest potential gradient is located well under the gate, in contrast with the case of the thinner-body structure in Fig. 8.

Fig. 10 Comparison of the electron temperature vs. distance along the center of the double-gate MOSFET body, for thin vs. thick body.

Fig. 11 Simulated impact ionization induced electron-hole-pair generation rate in a double-gate MOSFET (L<sub>g</sub>=79nm) vs. body thickness. The impact ionization rate is reduced by thinning the body.

Fig. 12  $V_T$  shift measured after each stress interval.  $|l_{dsa}t|$  is decreased for measurement with swapped S/D.

Fig. 13 Hot-carrier DC lifetime for CMOS FinFETs (P+ poly-Si<sub>0.6</sub>Ge<sub>0.4</sub> gate, no hydrogen anneal after fin etch).

Fig. 14 Hot-carrier DC lifetime for CMOS FinFETs (N+ poly-Si gate), showing the benefit of a hydrogen anneal (5 @ 900°C) after fin etch.

Fig. 15 Fig. 15 Effect of substrate temperature on relative  $I_{dsat}$  shift with stress time, for NMOS FinFETs.

Fig. 16 Effect of substrate temperature on relative I<sub>dsat</sub> shift with stress time, for PMOS FinFETs.

Fig. 17 Q<sub>BD</sub> distributions for CMOS FinFETs (P+ poly-Si<sub>0.6</sub>Ge<sub>0.4</sub> gate, no hydrogen anneal after fin etch). Q<sub>BD</sub> is extremely high for very small gate areas.

Fig. 18  $Q_{BD}$  distributions for CMOS FinFETs (N+ poly-Si gate).  $Q_{BD}$  is higher and more tightly distributed for devices which received a post-fin-etch anneal in hydrogen to smoothen the fin sidewall surfaces.