# Sub-1-V Supply Self-Adaptive CMOS Image Sensor Cell With 86-dB Dynamic Range

Sungsik Lee and Kyounghoon Yang, Senior Member, IEEE

Abstract—This letter presents a high dynamic range CMOS active pixel structure operating at a sub-1-V supply voltage, which is implemented using a standard 0.18-\$\mu\$m CMOS logic process. In order to improve the output voltage swing range and associated pixel dynamic range at a low supply voltage, a pMOS reset structure is incorporated into the pixel structure along with a photogate pixel structure based on the self-adaptive photosensing operation. At a low supply voltage of 0.9 V, the new pixel provides an output voltage swing range of 0.41 V and a high dynamic range of 86 dB, which is the highest among the reported pixel structures up to date operating at sub-1-V.

*Index Terms*—Adaptive sensitivity, CMOS active pixel sensor (CAPS), high dynamic range, low supply voltage.

#### I. Introduction

THE LOW-VOLTAGE operation of CMOS active pixel sensors (CAPSs) has been a key performance requirement for portable devices, such as personal digital assistants, cell phones, and digital still cameras [1]-[3]. The pinned photodiode (PPD)-based four-transistor pixel is widely used in CAPSs due to the low noise level and high sensitivity [2], [3]. However, the PPD-based pixels have shown some limitations in pixel operation especially at low voltage mainly due to the incomplete charge transfer and difficulty of full depletion in the PPD, which result in a high random noise level [1]–[3]. As a result, the conventional three-transistor (3-T) pixel structure is usually favored for a low-voltage pixel operation due to the larger room for the optimal biasing condition. However, it has also been found that the performances of the 3-T pixel such as the output voltage swing range and dynamic range are significantly degraded with downscaling of the supply voltage [4]-[6]. As an approach to increase the output voltage swing range and the related dynamic range of conventional 3-T pixel sensors, bootstrapped reset pulse techniques have been proposed [5], [6]. The limitation associated with the bootstrapping technique is that it can give rise to the hot-carrier-related reliability problems in a submicrometer technology, which significantly reduces the circuit lifetime [6]. Another approach to achieve a low-voltage operation is to use a complementary active pixel structure [7], which can allow pixel operation at a supply

Manuscript received January 3, 2007; revised March 13, 2007. The review of this letter was arranged by Editor P. Yu.

S. Lee was with Korea Advanced Institute of Science and Technology (KAIST), Daejeon 305-701, Korea. He is now with Electronics and Telecommunications Research Institute (ETRI), Daejeon 305-350, Korea (e-mail: lss@etri.re.kr).

K. Yang is with the School of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon 305-701, Korea (e-mail: khyang@ee.kaist.ac.kr).

Digital Object Identifier 10.1109/LED.2007.896885

voltage in a range of 1 V. However, the complementary active pixel structure shows a low dynamic range and an increased pixel complexity. As another approach to increase the dynamic range, the logarithmic 3-T pixel structure has been proposed [8], but its small output voltage swing range and large dark current level usually result in a low signal-to-noise ratio and low sensitivity at low illumination intensity [9].

In this letter, a new pixel structure with a high dynamic range operating at a sub-1-V supply is proposed and implemented based on a self-adaptive photosensing operation using a standard 0.18- $\mu$ m CMOS logic process. To achieve these performances, a pMOSFET is incorporated in the new pixel design as a reset transistor along with the optimized self-adaptive photogate active pixel structure [10], [11]. The details of the pixel structure and performance characteristics are discussed in the following sections.

#### II. NEW PIXEL STRUCTURE AND OPERATION

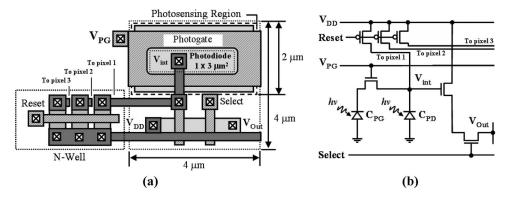

The schematic layout of the new pixel with a shared pMOSFET is illustrated in Fig. 1(a). A new photogate pixel structure is incorporated into the new pixel design for the optimized self-adaptive photosensing operation [8]. As shown in Fig. 1(a), a typical pMOSFET in an N-well structure is used as a reset transistor to increase the output voltage swing range [6], [12]. The pMOSFET is located only at one end of each row in a  $3 \times 3$  test array, so that the fill factor is not reduced by using a proper layout design. The layout of the proposed pixel structure can be further optimized for larger-scale pixel arrays. In order to reduce the dark current, the photodiode region of the pixel is surrounded by the photogate structure to isolate from the defective shallow trench isolation region, as shown in Fig. 1(a) [10], [13]. The conceptual equivalent circuit diagram of the new pixel structure is shown in Fig. 1(b). The basic operating principle of the new pixel is the same as that of the previously demonstrated pixel structure [10]. The new pixel structure can provide the self-adaptive photosensing operation, which also allows to increase the well capacity  $(Q_{\text{well}})$  by a large value of  $C_{\rm int}$  [10]. For the proposed pixel structure, the enhanced dynamic range can be obtained from the significantly increased  $Q_{\text{well}}$  as well as the reduced dark current level by the optimized photogate design. A positive bias voltage  $(V_{PG})$  is applied at the photogate for optimizing the high dynamic range based on the self-adaptive photosensing operation [10]. For the reset operation, a reset voltage of 0 V is applied at the gate of the pMOSFET [6]. Hence, the new pixel can exhibit a high dynamic range and a wide output voltage swing range at a given supply voltage.

Fig. 1. (a) Schematic layout (pixel area:  $4 \times 4 \mu m$ , photosensing area:  $4 \times 2 \mu m$ , photodiode area:  $3 \times 1 \mu m$ ) and (b) conceptual equivalent circuit diagram of the new pixel structure ( $V_{\text{int}}$ : integration node voltage,  $C_{\text{PG}}$ : depletion layer capacitance of the photogate, and  $C_{\text{PD}}$ : depletion capacitance of the photodiode).

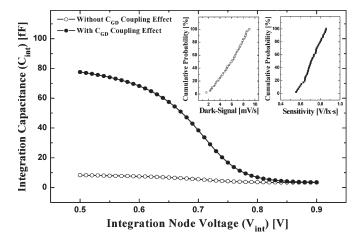

Fig. 2. Measured C–V characteristics with and without the gate-to-drain capacitance ( $C_{\rm GD}$ ) coupling effect for the case of  $V_{\rm PG}=0.9~\rm V$ . The inset shows the measured cumulative probabilities of the dark signal and sensitivity at an illumination intensity level of 200 lx at  $V_{\rm PG}=0.9~\rm V$ .

## III. EXPERIMENTAL RESULTS AND DISCUSSIONS

Fig. 2 shows the measured capacitance–voltage (C-V) characteristics of  $C_{\rm int}$  versus  $V_{\rm int}$  at a photogate voltage of  $V_{\rm PG} =$ 0.9 V, where  $C_{\text{int}}$  represents an integration capacitance at the node of  $V_{\rm int}$  in Fig. 1(b). The new proposed pixel exhibits the dynamic capacitance characteristics of  $C_{\rm int}$ , which lead to the self-adaptive photosensing operation [10]. As shown in Fig. 2, the new pixel shows a large value of  $C_{\text{int}}$  at  $V_{\text{int}}$  below 0.7 V. This is mainly due to the contribution of the large gate-drain capacitance  $(C_{\rm GD} = C_{\rm OX} = \varepsilon_{\rm ox} \cdot A_{\rm PG}/T_{\rm OX})$  arising from a thin gate oxide thickness  $(T_{OX})$  to the internal node through the coupling with  $C_{\mathrm{PD}}$  [4], where  $C_{\mathrm{OX}}$  is the oxide capacitance of the photogate,  $\varepsilon_{ox}$  is the dielectric constant of the gate oxide, and  $A_{\rm PG}$  is the area of the photogate. At  $V_{\rm PG}=0.9$  V, the dynamic range of the proposed pixel is measured to be 86 dB for an integration time of 700  $\mu$ s, which shows a large improvement of more than 15 dB compared to the previously reported conventional pixels operating at a low-voltage supply, which are characterized at shorter integration time [4], [5], [7]. Since the dynamic range of the pixel structure is inversely proportional to the integration time [10], [12], the proposed pixel can show the more improved dynamic range in the application with the shorter integration time. The major factor in achieving the high dynamic range from the proposed pixel is found to be the sig-

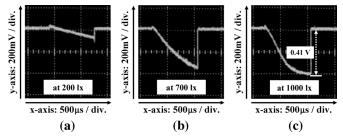

Fig. 3. Measured output voltage waveform at  $V_{\rm PG}=0.9~\rm V$  for the typical case of  $t_{\rm int}=700~\mu {\rm s}$  at illumination levels of (a) 200 lx, (b) 700 lx, and (c) 1000 lx (x-axis: time, y-axis: output voltage).

nificantly increased well capacity  $(Q_{\text{well}})$  due to the optimized photogate pixel design as characterized by the large  $C_{int}$  shown in Fig. 2. The inset shows the measured cumulative probabilities of dark signal and pixel sensitivity at an illumination intensity of 200 lx for the case of  $V_{\rm PG}=0.9$  V. The measured average dark signal at  $V_{\rm PG}=0.9$  V is 6.12 mV/s at 25 °C. This corresponds to a dark current density of 0.06 nA/cm<sup>2</sup>, which is 1.5 times lower than that of the previous other structures due to the optimized photogate layout design [4]–[7]. The measured average sensitivity at  $V_{PG} = 0.9 \text{ V}$  is  $0.69 \text{ V} \cdot \text{lx}^{-1} \cdot \text{s}^{-1}$ , which is comparable to other results [4]-[6], [11]. Fig. 3 shows the measured output voltage waveform at  $V_{\rm PG}=0.9~{

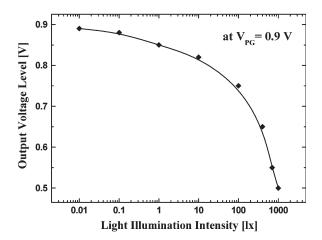

m V}$  for the typical case of  $t_{\rm int} = 700 \ \mu s$  at illumination levels of 200, 700, and 1000 lx. As shown in Fig. 3(b) and (c), the new pixel structure does not reach the saturation level even at the high illumination level of 700–1000 lx due to the self-adaptive nonlinear characteristics and shows saturation at 1000 lx [10]. The effects of pixel-to-pixel variation and fixed pattern noise can be compensated by using additional calibration circuitry and technique [10], [14], [15]. Fig. 4 shows the measured output voltage level versus light illumination intensity for the case of  $t_{\rm int} = 700~\mu {\rm s}$  at  $V_{\rm PG} = 0.9~{\rm V}$ . The dynamic range and voltage swing range of the proposed pixel structure are characterized and measured in the overall performance response including the linear and nonlinear regions as for the cases of CMOS image sensors based on an adaptive operation, such as logarithmic and linear-logarithmic pixel sensors [9], [16]. As shown in Fig. 4, the measured results for the new pixel structure demonstrate an output voltage swing range as large as 0.41 V due to the reset operation based on the pMOSFET structure [6]. These results clearly show that the new pixel structure is capable to

Fig. 4. Measured output voltage level versus light illumination intensity for the case of  $t_{\rm int}=700~\mu {\rm s}$  at  $V_{\rm PG}=0.9~{\rm V}$ .

$\label{table} TABLE\ \ I$  Performance Summary of the New Proposed Pixel Structure

| Parameters                 | Performance                              |

|----------------------------|------------------------------------------|

| Technology                 | Hynix 0.18-µm CMOS Process               |

| Pixel Size                 | 4 × 4 μm <sup>2</sup>                    |

| Effective Fill Factor      | 47 %                                     |

| Operating Voltage          | 0.9 V                                    |

| Photogate Bias Voltage     | 0.9 V                                    |

| Reset Pulse Height         | 0.9 V                                    |

| Output Voltage Swing-Range | 0.41 V                                   |

| Monochrome Sensitivity     | 0.69 V·lx <sup>-1</sup> ·s <sup>-1</sup> |

| Dynamic-Range              | 86 dB                                    |

| Dark-Signal                | 6.12 mV/s                                |

| Dark-Current               | 0.06 nA/cm <sup>2</sup>                  |

| Conversion Gain            | 96 μV/e                                  |

operate at a sub-1-V supply of 0.9 V with a large output voltage swing range. The pMOSFET structure shared in each row of the new pixel structure, which results in the increased output voltage swing range, is characterized to introduce a signal delay of about 0.3 ps in the reset operation between adjacent pixels at the same row. The effects of reset signal delay may need to be considered in the case of high-resolution image sensor applications but insignificant for other general applications of slow moving picture and still images with a long integration time in the range of 700  $\mu$ s. The overall performance characteristics of the new proposed pixel structure are summarized in Table I. The results demonstrate that the new self-adaptive pixel structure based on the pMOS reset operation provides the large output voltage swing range with a dynamic range of 86 dB, which is the highest dynamic range among the previously reported pixel structures operating at sub 1 V [4], [5], [7].

# IV. CONCLUSION

A new photogate pixel structure with a pMOSFET used as the reset transistor was proposed based on the standard CMOS logic process. At a low supply voltage of 0.9 V, the

new pixel provides a wide output voltage swing range of 0.41 V due to the pMOS reset operation. In addition, at an optimal photogate bias voltage of 0.9 V, the new pixel structure demonstrates the high dynamic range of 86 dB due to the employed self-adaptive photosensing operation. The results demonstrate that the proposed photogate pixel structure is very promising for low-voltage and high-dynamic-range CMOS image sensor applications.

#### ACKNOWLEDGMENT

The authors would like to thank H. Lee of KAIST for help on the measurement and characterization of pixel performance.

### REFERENCES

- [1] H. Abe, "Device technologies for high quality and smaller pixel in CCD and CMOS image sensors," in *IEDM Tech. Dig.*, 2004, pp. 989–992.

- [2] K. Mabuchi, N. Nakamura, E. Funatsu, T. Abe, T. Umeda, T. Hoshino, R. Suzuki, and H. Sumi, "CMOS image sensors comprised of floating diffusion driving pixels with buried photodiode," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2408–2416, Dec. 2004.

- [3] H. Takahashi, M. Kinoshita, K. Morita, T. Shirai, T. Sato, T. Kimura, H. Yuzurihara, S. Inoue, and S. Matsumoto, "A 3.9-μm pixel pitch VGA format 10-b digital output CMOS image sensor with 1.5 transistor/pixel," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2417–2425, Dec. 2004.

- [4] C. Shen, C. Xu, W. Q. Zhang, H. Rong, and M. Chan, "Low voltage CMOS active pixel sensor design methodology with device scaling considerations," in *Proc. IEEE Hong Kong Electron Devices Meeting*, May 2001, pp. 21–24.

- [5] H. S. Wong, R. T. Chang, E. Crabbé, and P. D. Agneelo, "CMOS active pixel image sensors fabricated using a 1.8 V, 0.25-μm CMOS technology," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 889–894, Apr. 1998.

- [6] K. B. Cho, A. Krymski, and E. R. Fossum, "A 1.2 V micropower CMOS active pixel image sensor for portable applications," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2000, pp. 114–115.

- [7] C. Xu, W. Ki, and M. Chan, "A low-voltage CMOS complementary active pixel sensor (CAPS) fabricated using a 0.25-\(\mu\)m CMOS technology," *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 398–400, Jul. 2002.

- [8] A. Bermak, A. Bouzerdoum, and K. Eshraghian, "A high fill-factor native logarithmic pixel: Simulation, design and layout optimization," in *Proc. ISCAS Dig. Tech. Papers*, 2000, pp. 293–296.

- [9] L. Lai, C. Lai, and Y. King, "A novel logarithmic response CMOS image sensor with high output voltage swing and in-pixel fixed-pattern noise reduction," *IEEE Sensors J.*, vol. 4, no. 1, pp. 122–126, Feb. 2004.

- [10] S. Lee and K. Yang, "High dynamic-range CMOS image sensor cell based on self-adaptive photosensing operation," *IEEE Trans. Electron Devices*, vol. 53, no. 7, pp. 1733–1735, Jul. 2006.

- [11] M. Kyomasu, "A new MOS imager using photodiode as current source," *IEEE J. Solid-State Circuits*, vol. 26, no. 8, pp. 1116–1122, Aug. 1991.

- [12] D. X. D. Yang, A. E. Gammal, B. Fowler, and H. Tian, "A 640 × 512 CMOS image sensor with ultrawide dynamic range floating-point pixellevel ADC," *IEEE J. Solid-State Circuits*, vol. 34, no. 12, pp. 1821–1834, Dec. 1999.

- [13] H. Cheng and Y. King, "An ultra-low dark current CMOS image sensor cell using n+ ring reset," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 538–540, Sep. 2002.

- [14] M. Loose, K. Meier, and J. Schemmel, "A self-calibrating single-chip CMOS camera with logarithmic response," *IEEE J. Solid-State Circuits*, vol. 36, no. 4, pp. 586–596, Apr. 2001.

- [15] S. Decker, R. D. McGrath, K. Brehmer, and C. G. Sodini, "A 256 × 256 CMOS imaging array with wide dynamic range pixels and column-parallel digital output," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 2081–2091, Dec. 1998.

- [16] G. G. Storm, J. E. D. Hurwitz, D. Renshaw, K. M. Findlater, R. K. Henderson, and M. D. Purcell, "Extended dynamic range from a combined linear-logarithmic CMOS image sensor," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp. 2095–2106, Sep. 2006.