# Molybdenum-Gate HfO<sub>2</sub> CMOS FinFET Technology

Daewon Ha, H. Takeuchi, Y.-K. Choi\*, T.-J. King, W.P. Bai\*, D.-L. Kwong\*, A. Agarwal\*, and M. Ameen\*

Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720 USA \*Dept. of Electrical Engineering and Computer Sciences, KAIST, Daejeon-City, Republic of Korea \*Dept. of Electrical and Computer Engineering, University of Texas, Austin TX 78712, USA \*Axcelis Technoloies Inc., Beverly, MA 01915, USA

Phone: 510.643.2558, Fax: 510.643.2636, Email: daewon@eecs.berkeley.edu

#### Abstract

CMOS FinFETs with molybdenum gate and HfO<sub>2</sub> gate-dielectric are reported. By tuning the gate work function via nitrogen implantation and employing a narrow fin width, low values of threshold voltage (0.28/-0.17 V) and sub-threshold swing (67.5/62.5 mV/dec) were achieved. The use of HfO<sub>2</sub> rather than SiO<sub>2</sub> as the gate dielectric reduces the gate leakage current density by several orders of magnitude, for EOT in the range 1.75-1.95 nm. The observed weak temperature dependence for both electron and hole mobilities ( $\mu_{eff} \sim T^{-0.95}$ ) is ascribed to soft phonon scattering.

#### Introduction

The double-gate FinFET is one of the most promising transistor structures for scaling CMOS technology to sub-10 nm gate lengths [1]. Integration of metal gate and high-k gate dielectric is desirable to reduce the equivalent gate-oxide thickness (EOT) while maintaining low gate leakage current, to improve transistor drive current and to relax the fin-width requirement for controlling short-channel effects [2-4]. In order to maximize carrier mobilities and avoid statistical dopant fluctuation effects on threshold voltage (V<sub>T</sub>), the body of a FinFET should be undoped; V<sub>T</sub> adjustment must be achieved by tuning the gate work function, in this case. Molybdenum (Mo) is a candidate gate material for future FD-SOI CMOS technology, because it is compatible with a standard CMOS process flow and its work function can be adjusted within the desired range (4.5-5.0 eV) via nitrogen implantation [5-7]. In this paper, the tunability of the Mo gate work function on HfO2 is demonstrated for the first time using FinFETs.

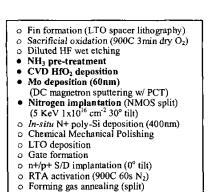

### **Device Fabrication**

Figure 1 outlines the FinFET process flow. UNIBOND® wafers were used as the starting substrates, and oxidized to reduce the SOI thickness to 50 nm. 80-nm wide Si fins were then defined by spacer lithography, while the source/drain (S/D) contact regions were defined by photolithography [8]. After patterning of the SOI and NH<sub>3</sub> pretreatment of the Si fin (110) sidewall surfaces, HfO<sub>2</sub> was deposited by CVD using Hf t-butoxide (Hf(OC(CH<sub>3</sub>)<sub>3</sub>)<sub>4</sub>) as a precursor at 500°C. A 60 nm-

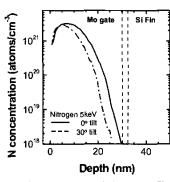

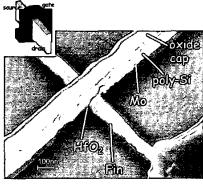

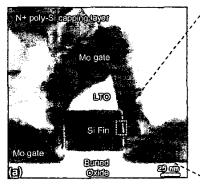

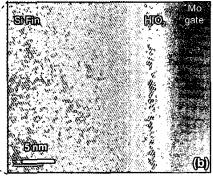

thick Mo film was then deposited by DC magnetron sputtering with a plasma charge trap (PCT) to minimize sputtering damage [9]. For some n-channel FinFETs, nitrogen (1x10<sup>16</sup> cm<sup>-2</sup>, 5 keV) was implanted into the Mo gate film at 30° tilt on each side of the Si fins (i.e., 60° tilt on the normal to the Mo gate surface) in order to reduce the effective Mo work function and achieve low V<sub>T</sub>. The use of a low-energy tilted implant prevents nitrogen penetration into the underlying gate dielectric (Figure 2). The Mo was capped with *in-situ* n+ doped poly-Si and planarized by CMP. After gate patterning and S/D ion implantation, a 900°C 60s RTA in N<sub>2</sub> was used to activate the dopants. Finally, the devices were annealed at 400°C in forming gas. Figure 3 is a tilted-view SEM image of a completed FinFET. It should be noted that no metallization or silicided S/D structure was used in this study. Figure 4 shows a cross-sectional TEM image, and a close-up view of the gate stack at the Si fin sidewall. The Mo gate layer is continuous at the bottom of the Si fin due to the improved step-coverage with PCT sputtering [9].

# Results and Discussion

A. Work Function Tuning of Mo Gate on HfO2

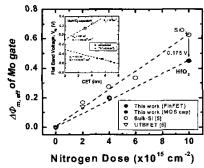

Figure 5 compares measured  $I_D\text{-}V_{GS}$  characteristics for Mogate  $HfO_2$  n-channel FinFETs with and without nitrogen gate implantation. It can be seen that  $V_T$  (defined as the gate voltage when  $I_D\text{=}100$  nA/ $\mu$ m for  $V_{DS}\text{=}50$  mV) is shifted from 0.73 V down to 0.28 V by the nitrogen implant. This indicates that the Mo-gate work function was effectively reduced by the nitrogen implant. Compared to our previous reports [5-7], the sub-threshold swing is greatly improved due to the minimization of Mo gate sputtering damage and the low-energy tilted nitrogen implantation [9]. The amount of reduction in gate work function is proportional to the nitrogen implant dose (Figure 6), but it is less for Mo on  $HfO_2$  than for Mo on  $SiO_2$  due to the Fermi-level pinning effect [10,11] and nitrogen diffusion into the  $HfO_2$ .

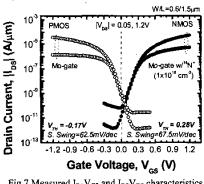

Figure 7 shows measured  $I_D$ - $V_{GS}$  and  $I_D$ - $V_{DS}$  characteristics for n-channel (with nitrogen-implanted Mo gate) and p-channel (with pure Mo gate) FinFETs. The  $V_T$  and sub-threshold swing values for the n-channel (p-channel) device are 0.28 (-0.17) V, and 67.5 (62.5) mV/dec, respectively. The p-channel

device exhibits higher parasitic resistance than the n-channel device due to differences in p-type vs. n-type dopant redistribution in thin SOI during RTA [12].

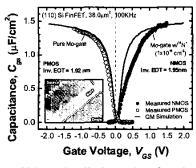

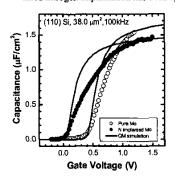

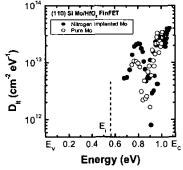

Figure 8 compares measured  $C_{G^{-}}V_{G}$  data (circles) with quantum-mechanical simulation (lines) [13]. The multi-fin device structure is shown in the inset. Extracted EOT in inversion is 1.95 or 1.92 nm for n-channel or p-channel devices, respectively. Stretch-out in the measured C-V characteristic is seen for the n-channel device, but not for the p-channel device. This result indicates an asymmetrical distribution of interface traps ( $D_{it}$ ) within the energy bandgap (i.e., higher  $D_{it}$  above  $E_i$ ) [14], which explains the larger sub-threshold swing of the n-channel FinFET (Figure 7). As shown in Figure 9, the deviation from the ideal C-V characteristic is larger for a nitrogen-implanted Mo gate, indicating a higher interfacial trap density. This is likely due to the formation of an interfacial  $HfO_xN_v$  layer at the Si surface [15].

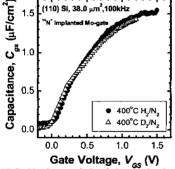

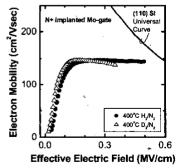

# B. Carrier Mobility

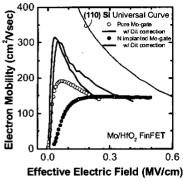

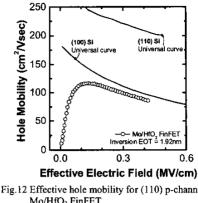

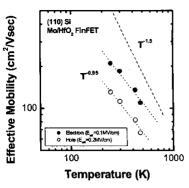

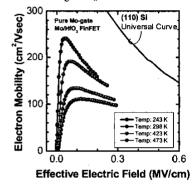

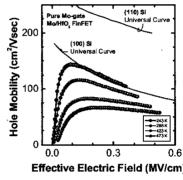

Figure 11 shows the field-effect electron mobility for (110) Si sidewall Mo/HfO<sub>2</sub> FinFETs with (lines) and without (symbols) correcting for interface trap density [16]. The apparent electron mobility is lower for the nitrogen-implanted device as compared to the unimplanted device, due to the higher interface trap density. Figure 12 shows the field-effect hole mobility for a (110) Si sidewall Mo/HfO2 FinFET. Both the electron mobility and the hole mobility are significantly degraded compared to the universal mobility curves for a (110) Si surface with SiO<sub>2</sub> gate dielectric [17]. In order to elucidate the reason for this, the carrier mobility dependence on temperature (in the range from -50°C to 200°C) was investigated. Both electron and hole mobilities increase with decreasing temperature due to reduced phonon scattering (Figure 13). However, at low field strength (0.1 MV/cm for electrons and 0.2 MV/cm for holes) they exhibit a weaker temperature dependence ( $\mu_{eff} \sim T^{-0.95}$ ) compared to mobilities for SiO<sub>2</sub> gate dielectric ( $\mu_{eff} \sim T^{-1.5}$ ), as shown in Figure 14. This indicates that the mobilities are limited by HfO2 soft phonon scattering [18,19]. Figure 15 shows that the peak electron mobility achieved in this work is comparable to previously published data for (100) Si with HfO<sub>2</sub> gate dielectric. This is notable because the electron mobility is lower for a (110) Si surface than for a (100) Si surface, with SiO2 gate dielectric.

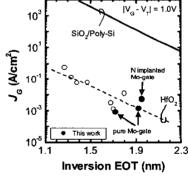

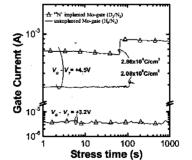

# C. HfO2 Gate Dielectric

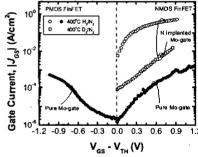

Figure 16 shows the measured gate leakage current density characteristics. Lower gate leakage is seen for the p-channel FinFET as compared to the n-channel FinFET (unimplanted Mo gate), due to the larger hole barrier height for HfO<sub>2</sub> [20]. Compared to a SiO<sub>2</sub>/poly-Si gate stack, the gate leakage current is reduced by 3-4 orders of magnitude for the same EOT (Figure 17). The nitrogen-implanted Mo-gate n-channel

FinFET shows increased gate current, likely due to nitrogen diffusion into the HfO<sub>2</sub> which degrades the interfacial and bulk properties of HfO<sub>2</sub> [15]. Deuterium annealing is effective to reduce the gate current by 1-2 orders of magnitude (Figure 16), and to improve the effective electron mobility slightly (Figure 19). This implies that deuterium can effectively passivate traps within HfO<sub>2</sub>N<sub>y</sub>. Figure 20 shows the gate dielectric charge-to-breakdown (Q<sub>BD</sub>) characteristics under constant voltage stressing. These initial results indicate that the reliability of a nitrogen-implanted Mo-gate device is comparable to that of a pure Mo-gate device. Key results are summarized in Table I.

### Summary

CMOS FinFETs with Mo gate on  $HfO_2$  are demonstrated for the first time. Low gate leakage current density was achieved for a thin inversion EOT (down to 1.72 nm), with carrier mobilities comparable to previously reported works (limited by soft phonon scattering).  $V_T$  adjustment is shown to be feasible by tuning the effective Mo work function via nitrogen implantation. Further process optimization is needed to prevent nitrogen diffusion into the  $HfO_2$ , to make Mo-gate  $HfO_2$  FinFET technology suitable for future nanoscale CMOS technology.

### Acknowledgement

This work is supported through the MARCO Focus Center on Material, Structures, and Devices under contract 2001-MT-887. FinFETs were fabricated in the UC Berkeley Microfabrication Laboratory, and staff support is gratefully acknowledged.

#### References

- [1] C. Hu, VLSI Technology Symp. Digest, pp. 4-5, 2004.

- [2] D. Frank et al., IEEE Elec. Dev. Lett., pp. 385-387, 1998.

- [3] B. Guillaumot et al., IEDM Digest, pp. 355-358, 2002.

- [4] R. Chau, IEEE Elec. Dev. Lett., pp. 1-3, 2004.

- [5] P. Ranade et al., IEDM Digest, pp. 363-366, 2002.

- [6] Y.-K. Choi et al., IEDM Digest, pp. 259-262, 2002.

- [7] D. Ha et al., Jpn. J. Appl. Phys., pp. 1972-1982, 2003.

- 8] Y.-K. Choi et al., IEEE Elec. Dev. Lett., pp. 25-27, 2002.

- [9] D. Ha et al., submitted to IEEE Trans. Elec. Dev., 2004.

- [10] Y. Yeo et al., IEEE Elec. Dev. Lett., pp. 342-344, 2002.

- [11] H. Takeuchi et al., to be presented in IEDM, 2004

- [12] H. Park et al., IEDM Digest, pp. 337-340, 1999.

- [13] Shred simulation (http://www.nanohub.org).

- [14] J.-P. Han et al., IEEE Elec. Dev. Lett., pp. 126-128, 2004.

- [15] K. Sekine et al., IEDM Digest, pp. 103-106, 2003.

- [16] W. Zhu et al., IEEE Trans. Elec. Dev., pp. 98-105, 2004.

- [17] S. Takagi et al., IEEE Trans. Elec. Dev., pp. 2363-2368, 1994.

- [18] M. Fischetti et al., J. Appl. Phys., pp. 4587-4608, 2001.

- [19] Z. Ren et al., IEDM Digest, pp. 793-796, 2003.

- [20] J. Robertson, J. Vac. Sci. Tech., pp. 1785-1791, 2000.

Fig.1 Process sequences for Mo/HfO2 FinFETs.

Fig.2 Simulated implanted nitrogen profiles in the Mo/HfO<sub>2</sub> stack (dose =  $5 \times 10^{15}$  cm<sup>-3</sup>).

Fig.3 Tilted-view SEM image of Mo/HfO2 FinFET.

W/L=0.6/1.5µm V...=0.06.1.2V Drain Current (A/μm) 10 101 -0.3 0.0 0.3 0.6 0.9 1.2 Gate Voltage (V)

Fig. 4 (a) Cross-section TEM image and (b) close-up of Mo-gate and HfO2 interface after 900C 60s in N<sub>2</sub> ambient. The Mo gate was implanted with nitrogen to a dose of 1x10<sup>16</sup> cm<sup>-2</sup>.

Fig.5 Nitrogen implantation into Mo is effective for V<sub>T</sub> control without degrading sub-threshold swing.

W/L≃0.6/0.5μm

Fig.6 Change in effective gate work function vs. nitrogen implantation dose

NMOS PMOS Current, Ilps (μΑ/μπ 50 -1.2 -0.9 -0.6 -0.3 0.0 0.3 0.6 0.9 Drain Voltage,  $V_{DS}$  (V)

Fig.7 Measured  $I_D\text{-}V_{OS}$  and  $I_D\text{-}V_{DS}$  characteristics of CMOS FinFETs. Low energy (5 KeV) and  $30^{\rm o}$  tilted nitrogen implantation has been applied to the Mo gate for the n-channel FinFET.

Fig. 8 Measured C<sub>G</sub>-V<sub>G</sub> characteristics for n-channel Fig. 9 Comparison of n-channel C<sub>G</sub>-V<sub>G</sub> characteristics Fig. 10 Extracted interface trap density for pure and p-channel Mo/HfO2 FinFETs.

with and without nitrogen implantation.

(O) and N-implanted ( ) Mo/HfO2

Fig.11 Effective electron mobility for (110) nchannel Mo/HfO2 FinFETs with and w/o correcting for Dir.

Fig.12 Effective hole mobility for (110) p-channel Mo/HfO<sub>2</sub> FinFET.

(110) Si

—O— Mo/HfO, FinFET Inversion EOT = 1.92nm

Fig.14 Electron and hole mobilities for HfO2 FinFETs show weaker dependence on temperature, than for SiO<sub>2</sub> (T<sup>-1.5</sup>) devices.

Effective Electric Field (MV/cm)

Electron Mobility (cm $^2$ /V sec) 200 100 (110) Si L (100) Si (100) Si Peak 2.0 Inversion EOT (nm)

Fig. 13 Effective (a) electron and (b) hole mobility at various measurement temperatures.

Fig.15 Peak electron mobility vs. inversion EOT.

Fig.16 Gate leakage current characteristics for nand p-channel Mo/HfO2 FinFETs. D2 annealing is effective to reduce Igate.

Fig.17 EOT (inversion) vs. gate leakage current.

Fig. 18 C<sub>G</sub>-V<sub>G</sub> characteristic of nitrogen implanted Mo gate device for different forming gas annealing. Table I. Key device results of Mo/HfO2 FinFETs

Fig.19 Effective electron mobility for different forming gas annealing.

Fig.20 Gate dielectric breakdown characteristic for nchannel Mo/HfO2 FinFET

PMOS NMOS Low V<sub>T</sub> High V<sub>T</sub> Low V<sub>T</sub> 14N+ implant (cm<sup>-2</sup>) 1x1016 Measured V<sub>T</sub> (V) -0.17 0.28 0.73 (@100nA/µm) 62.5 S. Swing (mV/dec) 67.5 72.6 1.75 1.92 Inv. EOT (nm) 1.95 Jgate (mA/cm<sup>2</sup>) 5.55 0.52 146.7 191.9 115.9 Peak mobility (cm<sup>2</sup>/V sec)

27.5.4